Almacenamiento en STM32 DISCO-L476VG

Plataforma de evaluación HW para STM32L4

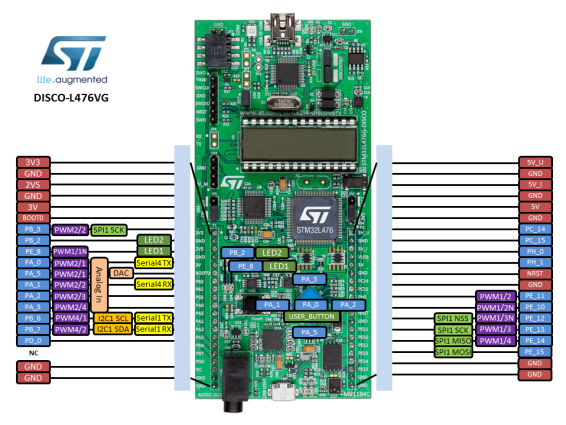

DISCO-L476VG

Placa de desarrollo STM32 Discovery kit //32L476GDISCOVERY// con MCU STM32L476VG

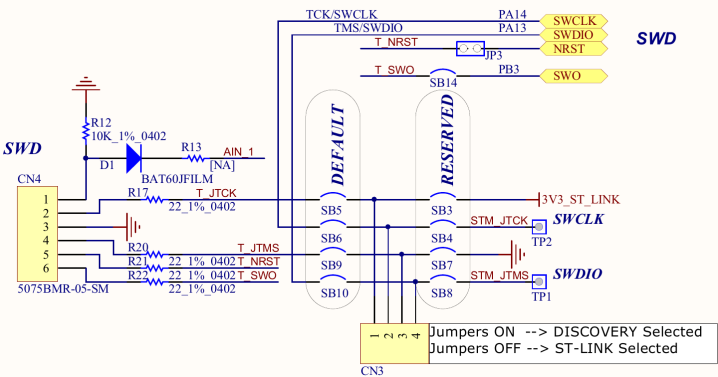

- Depurador/programador en PCB ST-LINK/V2-1 con conector SWD

- Alimentación (4x opciones):

- ST-LINK/V2-1

- Conector USB FS

- Externa 5 V

- Batería CR2032

- 2x LEDs de usuario: LD4 (rojo), LD5 (verde)

- 2x botón pulsador: USER y RESET

- 1x puerto USB OTG FS con conector micro-AB, capacidad de re-enumeración USB y 3x interfaces USB:

- VCP (Virtual Com port)

- Almacenamiento masivo (USB Disk drive) para programación por arrastre

- Depuración (Debug port)

- 1x Joystick de 4x direcciones y selección central

- SAI Audio DAC, estéreo, con conector Jack de salida

- Micrófono digital MEMS

- Acelerómetro y magnetómetro MEMS

- Giróscopo MEMS

- 128-Mbit memoria Quad-SPI Flash

- Amperímetro de corriente del MCU con 4 rangos y auto calibración

MCU STM32L476VGT6 (encapsulado LQFP100)

- ARM®32-bit Cortex®-M4 CPU con FPU y acelerador ART

- 80 MHz frecuencia máxima de CPU

- VDD de 1.71V a 3.6 V

- 1 MB Flash

- 128 KB SRAM

- 114x GPIOs con capacidad de interrupción externa

- 3x 12-bit ADCs con 16 canales

- 2x 12-bit DAC

- 3x USART

- 2x UART

- 1x LPUART

- 2x SAI

- 3x I2C

- 3x SPI

- 1x Quad SPI

- 7x temporizadores (Timers) de propósito general, 2x básicos y 2x avanzados

- 2x temporizadores de bajo consumo (low-power)

- 2x temporizadores tipo Watchdog

- 1x CAN

- USB OTG FS

- SDMMC

- SWPMI

- LCD COM x SEG

- RTC

- TRNG (generador de aleatorios por HW)

- 21x sensores capacitivos

- 2x comparadores analógicos

- 2x amplificadores operacionales

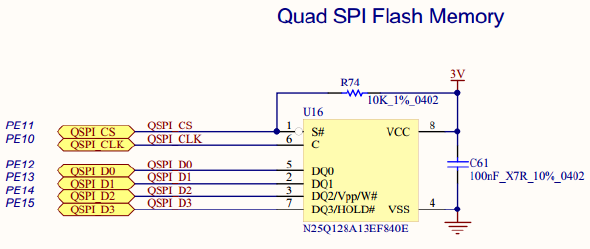

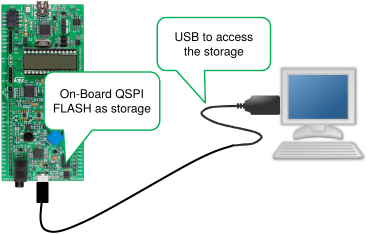

QuadSPI NOR Flash (16MB)

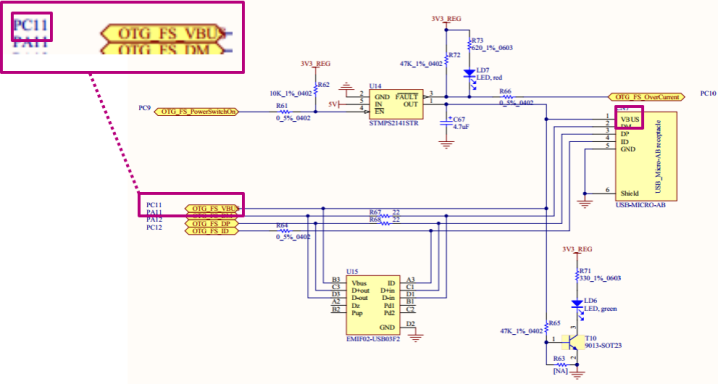

Interfaz USB OTG FS

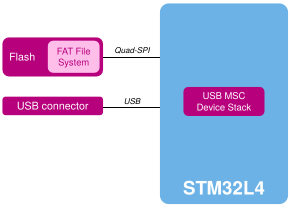

Desarrollo SW: almacenamiento

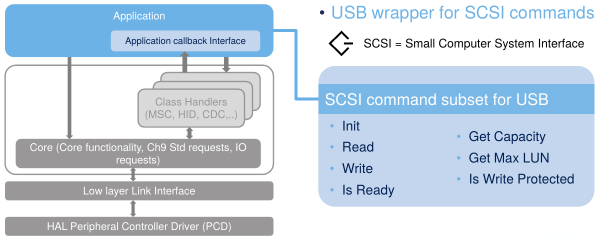

El objetivo del tutorial es la configuración y comunicación con dispositivos de almacenamiento externos a la MCU para la transferencia masiva de información, p.ej. para almacenamiento de audio para grabación/reproducción, y que en último término se organizará en archivos que podrán ser transferidos entre un PC y la memoria NOR-Flash externa incluida en la plataforma STM32L4Discovery. Para ello, haremos uso de la clase de almacenamiento masivo MSC (Mass Storage device Class) de USB incluida como MiddleWare de conectividad/multimedia, así como rutinas de BSP basadas en HAL para manejar la memoria Flash externa de tipo Quad-SPI.

Por otra parte, se incluyen en el tutorial demostraciones basadas en funciones de BSP, así como la habilitación de la interfaz de depuración SWD.

Creación del proyecto con STM32CubeMX

En este caso se hará un uso intensivo de FW de BSP para las interfaces GPIO (LEDs, JoyStick), LCD, MEMS (Gyro, Compass, Accelero) y de Audio (Mic_IN & SAI_OUT), por lo que no es necesario definir en detalle los periféricos implicados en CubeMX, si bien requiere una configuración manual en SW de los respectivos módulos HAL.

Respecto al uso de la memoria QSPI, veremos aquí como configurar con CubeMX, aunque finalmente también haremos uso de las funciones BSP facilitadas; y finalmente será necesario configurar el dispositivo USB de almacenamiento masivo desde CubeMX que relaciona directamente el Middleware de dicho protocolo en dispositivos USB.

Comenzamos entonces el tutorial como proyecto nuevo sin pines y vamos añadiendo en CubeMX sólo lo estrictamente necesario, el resto se aportará en BSP.

Configuración de depuración avanzada SWD

La interfaz de depuración (Debug) que normalmente establecemos como Serial Wire en la categoría SYS se amplía con un pin más (SWO, pin PB3) para poder uso de un visor avanzado incluido en Atollic TrueStudio, y se fija ahora con la opción Trace Asyncronous Sw. Este nuevo pin incluido (PB3) debe puentearse al pin SWO de la interfaz SWD, existe un puente abierto en el PCB que podría soldarse, si bien por ahora nos limitaremos a conectarlo con un cable como puede verse en la figura. Comprobamos también en esta categoría SYS que el temporizador base del sistema es el SysTick y dejamos por defecto el resto de opciones deshabilitadas.

Siguiendo los pasos indicados en el apartado //anterior// sobre la configuración propuesta:

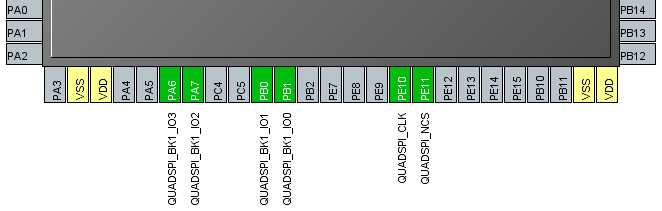

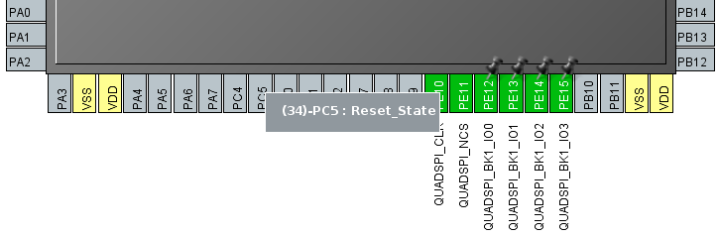

Configuración de memoria QSPI

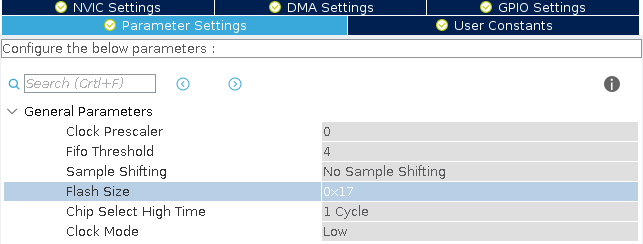

Categoría QUADSPI en conectividad (Connectivity), Single Bank: Quad SPI Line

Los pines asignados automáticamente son: PA6, PA7, PB0, PB1, PE10 y PE11, que no se corresponden al esquemático dl PCB mostrado con pines correlativos PE10-PE15, por lo que hay que re-mapearlos haciendo uso de posiciones alternativas con la tecla Ctrl.

En la configuración de parámetros: PSC a 0, umbral de FIFO a 4, y tamaño de la Flash a 0x17, equivalente a 24 en decimal, que es número de bits de direcciones para el tamaño de la Flash en bytes, en este caso 24 bits para 16 MB.

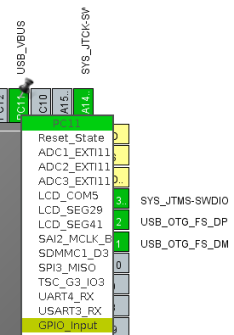

Configuración de USB

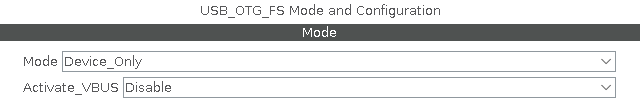

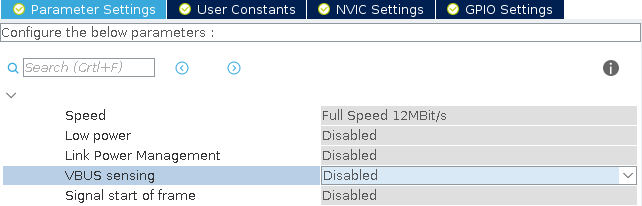

Categoría USB_OTG_FS en conectividad (Connectivity), Mode: Device_Only

Pines PA11 y PA12automáticos

Necesario definir de forma manual VBUS (pin PC11) como entrada, etiqueta USB_VBUS, según esquemático. Desde CubeMX la activación de VBUS asocia erróneamente el pin PA9.

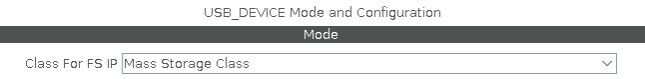

Categoría USB_DEVICE en Middleware, Class For FS IP: Mass Storage Class

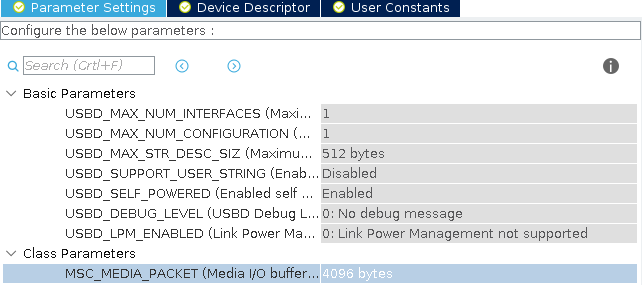

MSC_MEDIA_PACKET= 4096 bytes, ya que parar la memoria N25Q128A la granularidad sub-sector de borrado es de 4kB

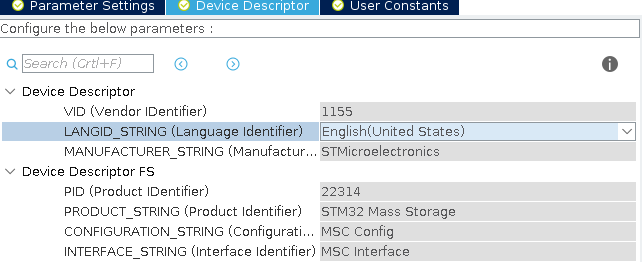

En el descriptor no son necesarios cambios:

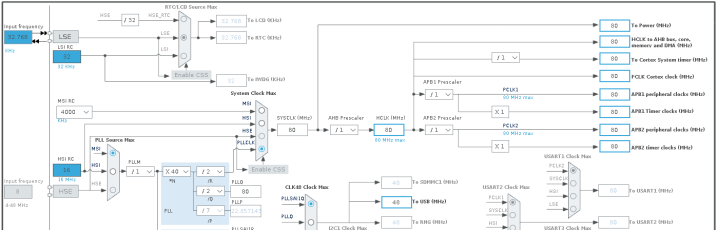

Configuración de relojes

Activa en categoría RCC del núcleo (System Core) el reloj externo LSE asociado a pines PC14 y PC15.

Comprobar que está activa la autocalibración para el MSI.

Comprobar reloj de USB a 48 MHz y máxima frecuencia de MPU a 80 MHz, el resto se configurará por BSP.

Código y modificaciones propuestas

Las fuentes del proyecto se incorporan en este caso a partir de uno pre-configurado y distribuido en Campus Virtual (SIlab7.zip) sobre el que se trabajará y ejecutará con puntos de ruptura establecidos en las rutinas destacadas.

Se propone el aprovechamiento de los distintos recursos facilitados en este proyecto para el almacenamiento de información estructurada de audio y movimiento a partir de los sensores, que requiera algún tipo de procesamiento posterior, p.ej. filtrado, promediado, etc.

dokuwiki\Exception\FatalException: Allowed memory size of 134217728 bytes exhausted (tried to allocate 20480 bytes)

An unforeseen error has occured. This is most likely a bug somewhere. It might be a problem in the authplain plugin.

More info has been written to the DokuWiki error log.