Verilog HDL

Verilog HDL

Verilog HDL es uno de los dos lenguajes de descripción de hardware (HDL, del inglés Hardware Description Language) más comunes que utilizan los diseñadores de circuitos integrados (IC), con una sintaxis derivada del lenguaje de programación C. Se corresponde inicialmente con el estándar IEEE 1364-1995, extendido posteriormente en IEEE 1364-2005, y finalmente integrado en SystemVerilog (IEEE 1800-2023).

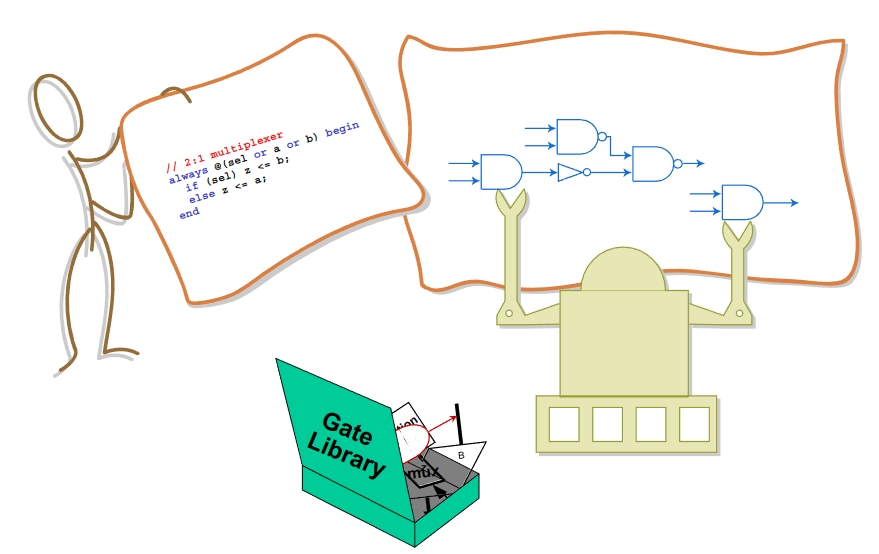

Un HDL permite la simulación del diseño en etapas tempranas del ciclo de desarrollo para corregir errores o experimentar con diferentes arquitecturas, llevar a cabo la síntesis lógica del mismo y facilitar la documentación del mismo. Los diseños descritos en HDL son independientes de la tecnología, fáciles de diseñar y depurar, y suelen ser más legibles que los esquemas, especialmente para circuitos grandes y complejos, lo que permite además un prototipado rápido y acelerar el tiempo de salida del producto final (TTM, del inglés Time-To-Market).